51

PROTOTIPAZIONE |

HARDWARE

EMBEDDED

59 • FEBBRAIO • 2016

sitivi programmabili Xilinx, di essere amplia-

ta attraverso la vasta gamma di schede add-on

ADI, progettate sia per la conversione ad alta ve-

locità sia per altre aree applicative. Un aspetto

importante delle opzioni di interfaccia è il sup-

porto, tramite l’interfaccia FMC, dello standard

JESD204B. Si tratta di un protocollo seriale,

creato da JEDEC per ridurre il numero di con-

nessioni tra convertitori dati ad alta velocità e

altri dispositivi, che sta rapidamente afferman-

dosi come interfaccia predefinita adottata da un

numero crescente di fornitori. L’IP per suppor-

tare l’interfaccia è inclusa nella piattaforma di

valutazione Xilinx.

Anche se disponibile da molti anni, lo standard

JESD204 si è evoluto in linea con gli incrementi

di velocità e di risoluzione dei convertitori dati;

ora, questa soluzione offre un numero di pin infe-

riore e un livello di velocità superiore rispetto alle

alternative esistenti, garantendo inoltre la scala-

bilità necessaria per soddisfare le esigenze futu-

re. La revisione originale, JESD204, ha definito

una velocità di trasmissione dati tra 312,5Mbit/s

e 3,125 Gbit/s, mentre la revisione JESD204B

offre una velocità di linea fino a 12,5Gbit/s. Xi-

linx dispone di una implementazione JESD204B,

chiamata LogiCORE, che supporta 12,5Gbit/s in

conformità alle specifiche, con un massimo di

16,5Gbit/s in configurazioni fino a 32 lane. L’IP

può essere configurata sia come trasmettitore sia

come ricevitore, consentendo l’interfacciamento

rispettivamente di DAC o ADC.

ADI ha ora adottato lo standard JESD204B an-

che nei suoi convertitori ad alta velocità, come

ad esempio il modello AD9250: un ADC doppio

che offre una risoluzione di 14 bit, un rapporto

di campionamento accelerato a 250Msample/s e

una gamma dinamica esente da spurie di 88dBc

a 185MHz AIN e 250ms/s. L’AD9250 è suppor-

tato dall’AD-FMCJESDADC1-EBZ, dotato di

due dei convertitori a doppio canale e di un’in-

terfaccia seriale JESD204B ad alta velocità che

permette di connettersi direttamente alle piatta-

forme di sviluppo Xilinx KC705, VC707 e ZC706.

Conversione ad alta velocità

La creazione di un sistema di acquisizione dati ad

alta velocità utilizzando la piattaforma di valuta-

zione Xilinx e le schede add-on FMC/PMOD di

ADI è assimilabile a un processo ‘plug and play’;

con uno sforzo di configurazione relativamente

basso, il tecnico è in grado di valutare l’hardware

ADI utilizzando la scheda FPGA semplicemente

eseguendo uno script incluso nel file .zip del pro-

getto di riferimento.

Ogni volta che lo script viene eseguito, i dati ven-

gono acquisiti e salvati in un file .csv per l’analisi

off-line. Selezionando la scheda aggiuntiva adatta

all’applicazione, è possibile effettuare la verifica

concettuale in una frazione del tempo richiesto dai

percorsi progettuali convenzionali.

Per supportare questo metodo di design, ADI of-

fre schede add-on per un vasto insieme dei suoi

dispositivi ADC e DAC, unitamente al materiale

di riferimento per completare il progetto e permet-

terne la valutazione utilizzando la piattaforma Xi-

linx. Il tutto include dispositivi con ADC e DAC su

un’unica scheda che consentono la realizzazione di

un intero sistema di acquisizione dati. Un esempio

è il modulo AD-FMCDAQ2-EBZ, una soluzione a

banda larga in formato FMC di acquisizione e sin-

tesi di segnale. In definitiva, i sistemi di prototipa-

zione rapida ad alta velocità possono presentare

molte sfide; configurare l’hardware non dovrebbe

essere una di queste. Adottando un approccio mo-

dulare per la verifica concettuale e la prototipazio-

ne, gli ingegneri possono passare dal concetto al

risultato finale in tempi ridotti, garantendo una

maggiore affidabilità del progetto oltre alla possi-

bilità di fornire rapidamente risultati reali e tan-

gibili di notevole interesse.

La combinazione tra convertitori dati ad alta ve-

locità e dispositivi programmabili ad alte presta-

zioni mette a disposizione dei team di progettazio-

ne che cercano di soddisfare le esigenze dei loro

mercati di riferimento un vantaggio sicuramente

significativo.

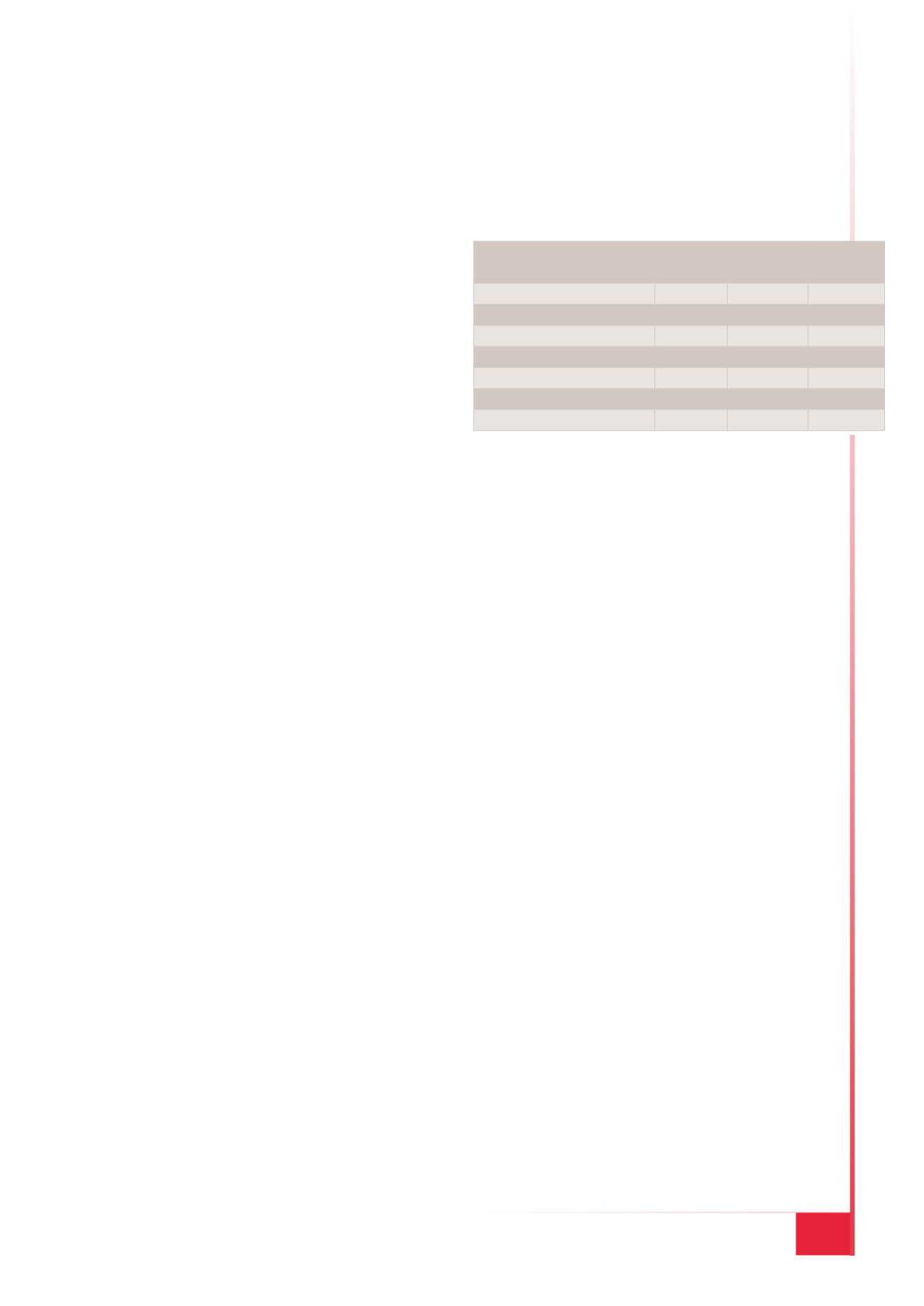

Tabella 1 - Il confronto tra le specifiche JESD204

Funzione

JESD204 JESD204A JESD204B

Rilascio Specifica

2006

2008

2011

Velocità massima lane (Gbps)

3,125

3,125

12,5

Lane multiple

No

Sì

Sì

Sincronizzazione lane

No

Sì

Sì

Sincronizzazione multi-device

Sì

Sì

Sì

Latenza deterministica

No

No

Sì

Clocking su armonica

No

No

Sì